- Produits

- Catalogues

- News & Trends

- Salons

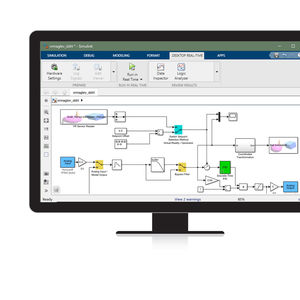

Logiciel de conception Simulink Design Verifier™de diagnosticde vérification

Ajouter à mes favoris

Ajouter au comparateur

Caractéristiques

- Fonction

- de conception, de diagnostic, de vérification

Description

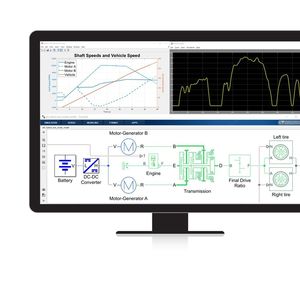

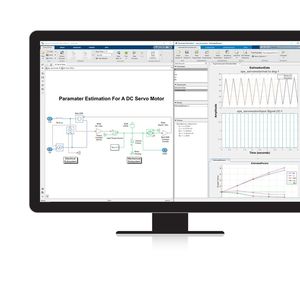

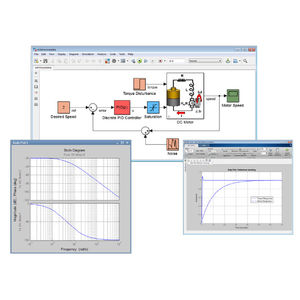

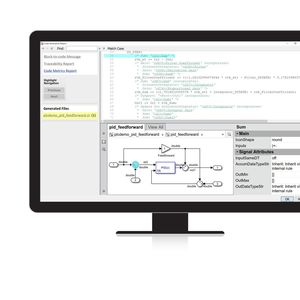

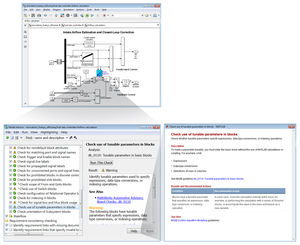

Simulink Design Verifier™ utilise des méthodes formelles pour identifier les erreurs de design cachées dans les modèles. Il détecte les blocs au sein du modèle qui entraînent des erreurs telles que les dépassements de capacité pour les entiers, la logique morte, les violations d'accès aux tableaux et les divisions par zéro. Il peut vérifier formellement que le design est conforme aux exigences fonctionnelles. Pour chaque erreur de design ou non-respect des exigences, il génère un cas de test de simulation permettant le débogage.

Simulink Design Verifier génère des cas de test pour la couverture de modèle et des objectifs personnalisés afin d'étendre les cas de test basés sur les exigences existants. Grâce à ces cas de test, vous pouvez vous assurer que votre modèle satisfait aux conditions, décisions, conditions/décisions modifiées (MCDC) et objectifs de couverture personnalisés. Outre les objectifs de couverture, vous pouvez définir des objectifs de test personnalisés afin de générer automatiquement des cas de test basés sur les exigences.

Le support des normes industrielles est assuré via l’IEC Certification Kit (for ISO 26262 and IEC 61508) et le DO Qualification Kit (for DO-178 and DO-254).

VIDÉO

Catalogues

Recherches associées

- Solution logicielle d'automatisation

- Solution logicielle de gestion

- Solution logicielle d'analyse

- Solution logicielle de process

- Solution logicielle Windows

- Solution logicielle de commande

- Logiciel de CAO

- Solution logicielle temps réel

- Logiciel en ligne

- Solution logicielle de conception

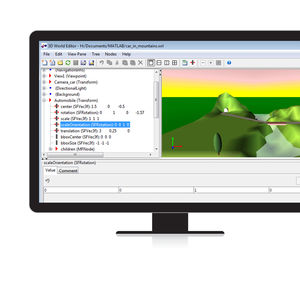

- Solution logicielle 3D

- Logiciel de mesure

- Logiciel de simulation

- Solution logicielle de visualisation

- Logiciel de programmation

- Logiciel automatisé

- Solution logicielle de réseau

- Logiciel de machine

- Logiciel d'ingénierie

- Logiciel de test

* Les prix s'entendent hors taxe, hors frais de livraison, hors droits de douane, et ne comprennent pas l'ensemble des coûts supplémentaires liés aux options d'installation ou de mise en service. Les prix sont donnés à titre indicatif et peuvent évoluer en fonction des pays, des cours des matières premières et des taux de change.