- Produits

- Catalogues

- News & Trends

- Salons

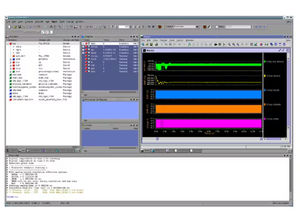

Logiciel d'analyse Vista™ Flowde modélisationde conceptionde création

Ajouter à mes favoris

Ajouter au comparateur

Caractéristiques

- Fonction

- d'analyse, de modélisation, de conception, de création, d'optimisation, d'évaluation, de débogage, de prototypage

- Applications

- d'architecture, d'écoulement

Description

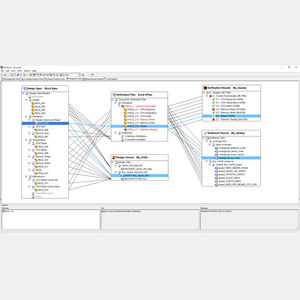

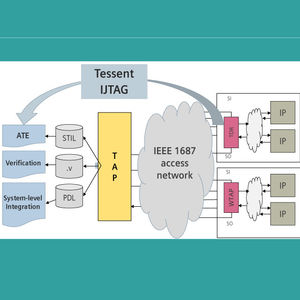

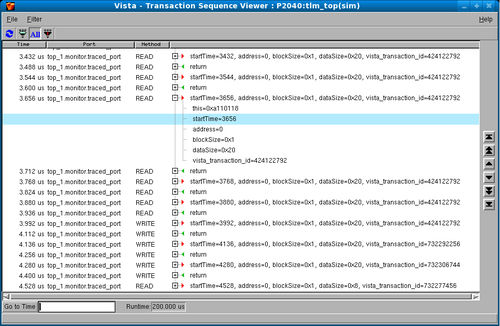

Le flux Vista comprend les étapes généralement utilisées par les architectes SoC, les ingénieurs matériels et les ingénieurs logiciels pour créer des modèles TLM, assembler et configurer le système, simuler, vérifier et déboguer, analyser et optimiser les performances, ainsi que l'alimentation et l'intégration avec le logiciel.

Prototypage, débogage et analyse de systèmes complexes

La méthodologie de conception ESL permet aux ingénieurs d'effectuer des optimisations sur les conceptions avancées d'aujourd'hui de manière plus rapide, plus efficace et plus rentable grâce au prototypage, au débogage et à l'analyse de systèmes complexes avant l'étape RTL. La méthodologie ESL et RTL permet de poursuivre le cycle de conception.

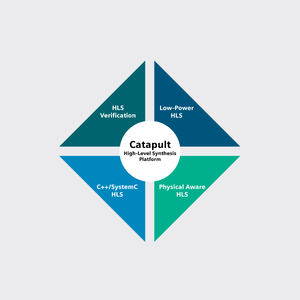

Explorer rapidement des alternatives de micro-architecture complexes

Vista Model Builder automatise la modélisation des fonctionnalités avec un ensemble de classes TLM et une couche de commodité pour une modélisation comportementale plus efficace et guidée. Un squelette de code TLM est automatiquement dérivé/généré à partir d'un ensemble de ports, de registres et de déclarations de mémoire, générant un code source SystemC compact conforme à TLM 2.0, afin que les utilisateurs puissent modéliser le comportement interne par eux-mêmes.

Environnement Vista Architect

Vista Architect offre un ensemble de modèles génériques rapides pour l'assemblage initial de la plate-forme et la validation précoce. Tous les modèles sont conformes à TLM 2.0 et peuvent être instanciés en tant que blocs de construction via un format textuel ou un format de schéma fonctionnel pour l'assemblage de n'importe quelle plate-forme cible.

---

Catalogues

Aucun catalogue n’est disponible pour ce produit.

Voir tous les catalogues de SIEMENS EDARecherches associées

- Solution logicielle d'automatisation

- Solution logicielle de gestion

- Solution logicielle d'analyse

- Solution logicielle de process

- Solution logicielle Windows

- Solution logicielle de commande

- Logiciel de CAO

- Solution logicielle temps réel

- Logiciel en ligne

- Solution logicielle de conception

- Solution logicielle 3D

- Logiciel d'interface

- Logiciel de mesure

- Logiciel pour l'industrie

- Logiciel de qualité

- Logiciel de simulation

- Solution logicielle de visualisation

- Logiciel automatisé

- Logiciel de développement

- Solution logicielle de réseau

* Les prix s'entendent hors taxe, hors frais de livraison, hors droits de douane, et ne comprennent pas l'ensemble des coûts supplémentaires liés aux options d'installation ou de mise en service. Les prix sont donnés à titre indicatif et peuvent évoluer en fonction des pays, des cours des matières premières et des taux de change.