- Électricité - Électronique

- Composant Électronique

- Microcontrôleur 32 bits

- e2v scientific instruments

- Produits

- Catalogues

- News & Trends

- Salons

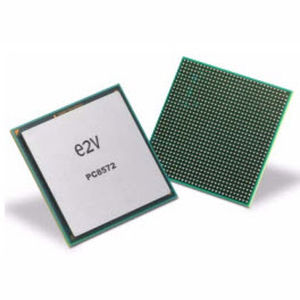

Microcontrôleur 32 bits TS68EN360

Ajouter à mes favoris

Ajouter au comparateur

Caractéristiques

- Type

- 32 bits

Description

Caractéristiques

• Processeur de CPU32+ (4,5 MIPS à 25 mégahertz)

– version à 32 bits du noyau CPU32 (entièrement compatible avec le CPU32)

– Le fond corrigent le mode

– adressage Octet-mauvais

• Jusqu'à bus de données à 32 bits (classement par taille dynamique d'autobus pour 8 et 16 bits)

• Jusqu'à 32 lignes d'adresse (au moins 28 toujours disponibles)

• Conception statique complète (opération de 0 - 25 mégahertz)

• Mode slave pour désactiver CPU32+ (permet l'utilisation avec les processeurs externes)

– QUICCs multiple peut partager un bus système (un maître)

– Le mode du compagnon TS68040 permet à QUICC d'être une puce du compagnon TS68040 et un périphérique intelligent

(22 MIPS à 25 mégahertz)

– Périphérique de TSPC603e (voir la note de DC415/D)

• Quatre minuteries polyvalentes

– Surensemble des minuteries MC68302

– Quatre minuteries de 16 bits ou deux minuteries à 32 bits

– Le mode de porte peut activer/le compte

• Deux DMAs indépendant (IDMAs)

• Module d'intégration de système (SIM60)

• Module de processeur de transmissions (CPM)

• Quatre Baud Rate Generators

• Quatre SCCs (Ethernet/IEEE 802,3 facultatif sur l'appui de SCC1-Full 10 Mbps)

• Deux SMC

• VCC = ± 5% de +5V

• fmax = 25 mégahertz et 33 mégahertz

• Température ambiante militaire : -55°C < COMITÉ TECHNIQUE < +125°C

• Palladium = 1.4W à 25 mégahertz ; 5.25V

2W à 33 mégahertz ; 5.25V

Description

Le contrôleur de la transmission TS68EN360 intégré par quadruple (QUICC™) est un microprocesseur intégré parpuce souple

et combinaison périphérique qui peut être employée dans un grand choix d'applications de contrôleur. Elle excelle en particulier dans les communications

activités. Le QUICC (prononcé « rapide ") peut être décrit comme TS68302 de la deuxième génération avec une plus haute performance en tout

domaines d'opération de dispositif, de flexibilité accrue, de prolongements importants dans la capacité, et d'intégration plus élevée.

---

Catalogues

Aucun catalogue n’est disponible pour ce produit.

Voir tous les catalogues de e2v scientific instrumentsAutres produits e2v scientific instruments

Semiconductors

Recherches associées

- Circuit intégré amplificateur de signal

- Module émetteur-récepteur

- Émetteur-récepteur RF

- Amplificateur à faible bruit

- Microcontrôleur

- Circuit intégré amplificateur RF

- Capteur d'image CMOS

- Capteur d'imagerie infrarouge

- Convertisseur programmable

- Émetteur-récepteur de faible puissance

- Circuit intégré convertisseur ADC

- Circuit intégré convertisseur haut débit

- Capteur d'image visible

- Microcontrôleur 32 bits

- Capteur d'image à haute vitesse

- Circuit intégré convertisseur DAC

- Circuit intégré convertisseur multivoie

- Amplificateur d'isolement

- Capteur d'image de haute sensibilité

- Capteur d'image proche infrarouge

* Les prix s'entendent hors taxe, hors frais de livraison, hors droits de douane, et ne comprennent pas l'ensemble des coûts supplémentaires liés aux options d'installation ou de mise en service. Les prix sont donnés à titre indicatif et peuvent évoluer en fonction des pays, des cours des matières premières et des taux de change.