- Robotique - Automatisme - Informatique

- Informatique Industrielle

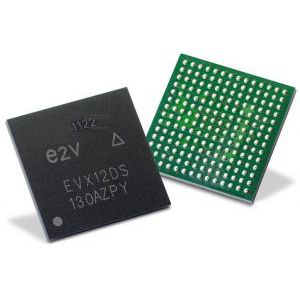

- Processeur 2 cœurs

- e2v scientific instruments

- Produits

- Catalogues

- News & Trends

- Salons

Processeur 2 cœurs PC8572E

Ajouter à mes favoris

Ajouter au comparateur

Caractéristiques

- Nombre de coeurs

- 2 cœurs

Description

CARACTÉRISTIQUES

- Deux cœurs e500 embarqués, évolutifs jusqu'à 1,5 GHz

- 6897 MIPS à 1500 MHz (Dhrystone estimé 2.1)

- Adressage physique 36 bits

- Prise en charge améliorée du débogage matériel et logiciel

- Unité à virgule flottante de double précision

- Unité de gestion de mémoire

- Cache L1/L2 intégré

- L1 Cache : 32 KB Data et 32 KB Instruction Cache avec

Support de verrouillage de ligne

- Cache L2 partagé : 1 Mo avec ECC

- Cohérence du matériel L1 et L2

- L2 Configurable comme SRAM, Cache et Transactions d'E/S peuvent être configurés

dans les régions d'antémémoire L2

- Contrôleur de mémoire DDR intégré avec support ECC complet,

Soutien :

- 333 MHz Débit d'horloge (667 MHz débit de données), 64 bits, 1,8 V

SSTL, DDR2 SDRAM

- Débit d'horloge 400 MHz (jusqu'à 800 MHz), 64 bits,

1.5V SSTL, DDR3 SDRAM SDRAM

- Plate-forme d'accélération des applications

- TLU avancé

- Moteur de sécurité intégré prenant en charge DES, 3DES, MD-5,

SHA-1/2, AES, RSA, RNG, Kasumi F8/F9 et ARC-4

Algorithmes de chiffrement

- PME intégrée (Expression régulière)

- Moteur de dégonflage des paquets

- Moteur de sécurité intégré avec XOR

- Quatre contrôleurs Ethernet sur puce à triple vitesse prenant en charge

Réseaux Ethernet/IEEE 802.3 10 et 100 Mbps, et 1 Gbps

avec MII, RMII, GMII, SGMII, RGMII, RTBI et TBI Physique

Interfaces et IEEE 1588

- Accélération de la somme de contrôle TCP/IP et QoS avancée

Caractéristiques

- Contrôle de flux sans perte

- E/S polyvalentes

- Interconnexion série RapidIO et PCI Express haut débit Interconnexion haut débit

Interfaces d'accès

- Tissu de commutation réseau sur puce (OCeaN)

- 133 MHz, 32 bits, 3,3 V E/S, bus local avec mémoire

Contrôleur

- Double contrôleur DMA intégré

- Double I

2

C et DUARTS

- Contrôleur d'interruption programmable

- IEEE 1149.1 JTAG Test Access Port (port d'accès de test JTAG)

- 1,1V Tension du noyau avec 3,3V/2,5V/1,8V E/S

- Ensemble PBGA 1023 broches

---

Catalogues

Aucun catalogue n’est disponible pour ce produit.

Voir tous les catalogues de e2v scientific instrumentsAutres produits e2v scientific instruments

Semiconductors

* Les prix s'entendent hors taxe, hors frais de livraison, hors droits de douane, et ne comprennent pas l'ensemble des coûts supplémentaires liés aux options d'installation ou de mise en service. Les prix sont donnés à titre indicatif et peuvent évoluer en fonction des pays, des cours des matières premières et des taux de change.