- Société

- Produits

- Catalogues

- News & Trends

- Salons

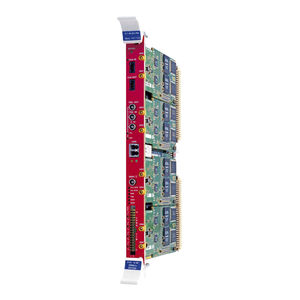

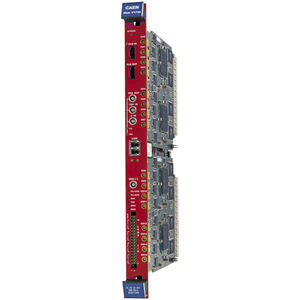

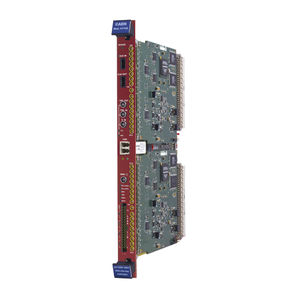

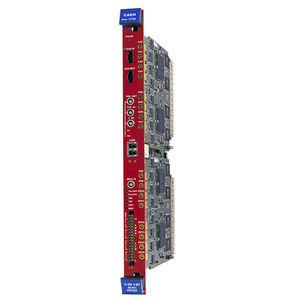

Numériseur jusqu'à 62.5 MS/s 64 canaux12 bitsPCIe

Ajouter à mes favoris

Ajouter au comparateur

Vous voulez acheter directement ?

Rendez-vous sur notre Shop.

Caractéristiques

- Vitesse

- jusqu'à 62.5 MS/s

- Nombre de canaux

- 64 canaux

- Spécifications

- 12 bits, PCIe, VME

Description

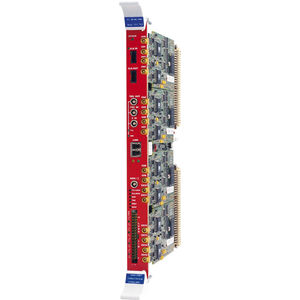

Le V1740 est un module VME 6U d'une largeur d'une unité abritant un numériseur de forme d'onde ADC Flash 64 canaux 12 bits 62,5 MS/s (65 MS/s en utilisant une horloge externe) et présentant une dynamique d'entrée de 2 Vpp (simple extrémité) sur deux connecteurs ERNI SMC. Des versions avec une gamme de pleine échelle d'entrée de 10 Vpp (single ended) sont également disponibles (V1740A/V1740C).

L'ajustement de l'offset DC (gamme ±1 V / 5 V) par des DACs 16bit programmables (un pour chaque groupe de 8 canaux) permet un échantillonnage correct d'une entrée analogique bipolaire (Vin = ±1 V / 5 V) jusqu'à une entrée positive (Vin = 0 ÷ +2 V / 10 V) ou négative (Vin = 0 ÷ -2 V / 10 V) sans perdre la résolution dynamique.

Le module dispose d'une entrée et d'une sortie d'horloge en face avant ainsi que d'une PLL pour la synthèse d'horloge à partir de références internes/externes. Le flux de données est continuellement écrit dans une mémoire tampon circulaire. Lorsque le déclenchement se produit, le FPGA écrit N échantillons supplémentaires pour le post-déclenchement et gèle le tampon qui peut être lu soit par VMEbus, soit par liaison optique. L'acquisition peut continuer sans temps mort dans un nouveau tampon.

Chaque canal dispose d'un SRAM Multi-Event Buffer divisible en 1 ÷ 1024 buffers de taille programmable. La lecture (par VMEbus ou Optical Link) d'un tampon gelé est indépendante des opérations d'écriture dans le tampon actif (stockage des données ADC). Deux tailles de mémoire numérique de canal sont disponibles en option : 192 kS/ch (mod. V1740/V1740C) et 1.5 MS/ch (mod. V1740A/V1740B).

Le V1740 prend en charge la synchronisation multicarte, ce qui permet à tous les CAN d'être synchronisés sur une source d'horloge commune et d'assurer l'alignement des horodatages de déclenchement. Une fois synchronisées, toutes les données seront alignées et cohérentes sur plusieurs cartes V1740.

---

Catalogues

Aucun catalogue n’est disponible pour ce produit.

Voir tous les catalogues de CAEN Spa* Les prix s'entendent hors taxe, hors frais de livraison, hors droits de douane, et ne comprennent pas l'ensemble des coûts supplémentaires liés aux options d'installation ou de mise en service. Les prix sont donnés à titre indicatif et peuvent évoluer en fonction des pays, des cours des matières premières et des taux de change.