- Société

- Produits

- Catalogues

- News & Trends

- Salons

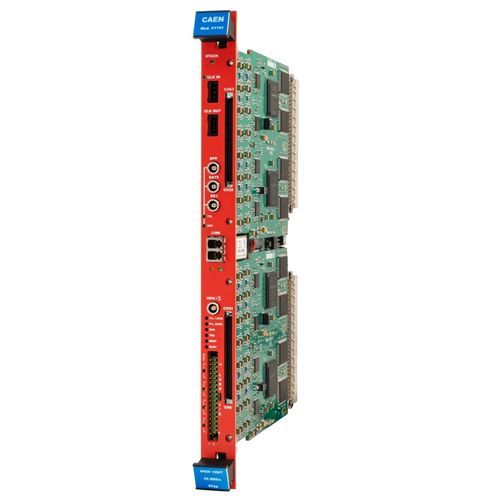

Redresseur de courant industriel V1741

Ajouter à mes favoris

Ajouter au comparateur

Caractéristiques

- Autres caractéristiques

- industriel

Description

module VME64 6U de 1 unité de largeur

1k, 2k, 4k 8k, 16k Peak Sensing ADC

64 canaux d'entrée, asymétriques, avec connecteur SMC ERNI à deux rangées de 68 broches (Zin : 2,5 kΩ)

Accepte les entrées positives et négatives

gamme pleine échelle de 4 Vpp ou 8 Vpp sélectionnable par logiciel (3,75 Vpp et 7,5 Vpp lorsque l'échelle mobile est activée)

Mode Common Gate (64 canaux convertis en même temps) avec largeur de porte linéaire ou programmable par logiciel

Faible temps mort (environ 50 ns après la fermeture de la porte précédente)

Algorithme d'échelle glissante pour la réduction des DNL

Suppression du zéro avec seuil programmable

Tampon multi-événements (1024 événements)

Interfaces de communication VME64 et liaison optique (protocole propriétaire CAEN CONET)

Pilotes Windows et Linux, bibliothèques C, logiciel de démonstration

Mise à jour du micrologiciel par l'utilisateur

Vue d'ensemble

Le V1741 est un CAN numérique à détection de crête appartenant à une nouvelle génération de systèmes de lecture de détecteurs basés sur une chaîne d'acquisition mixte analogique-numérique, combinant une haute densité de canaux (64 canaux) et un faible temps mort. L'architecture ADC FLASH permet d'obtenir un temps de conversion extrêmement faible de la crête d'impulsion, de sorte que les nouvelles conversions ont lieu moins de 50 ns après la fermeture des portes précédentes.

Le gain de conversion va de 1k à 16k canaux avec une faible non-linéarité différentielle (DNL) grâce à la méthode de l'échelle glissante.

Recevant le signal lent typique d'un préamplificateur sensible à la charge suivi d'un amplificateur de mise en forme (par exemple CAEN N1068), le FPGA identifie le pic de l'impulsion à l'intérieur d'une porte au moyen de filtres numériques. L'acquisition est commune à tous les canaux et a lieu dès que la porte arrive. La valeur de l'énergie ainsi que l'heure d'arrivée de l'événement sont d'abord stockées dans une mémoire tampon multi-événements de 1024

---

Catalogues

Aucun catalogue n’est disponible pour ce produit.

Voir tous les catalogues de CAEN SpaRecherches associées

- Alimentation électrique

- Alimentation électrique AC/DC

- Module convertisseur DC/DC

- Alimentation électrique ajustable

- Alimentation électrique à sorties multiples

- Alimentation électrique programmable

- Alimentation électrique monophasée

- Alimentation électrique rackable

- Convertisseur AC/DC

- Alimentation électrique AC/AC

- Alimentation électrique avec sortie USB

- Alimentation électrique 1U

- Convertisseur DC/DC de puissance

- Module d'alimentation d'E/S

- Contrôleur d'alimentation

* Les prix s'entendent hors taxe, hors frais de livraison, hors droits de douane, et ne comprennent pas l'ensemble des coûts supplémentaires liés aux options d'installation ou de mise en service. Les prix sont donnés à titre indicatif et peuvent évoluer en fonction des pays, des cours des matières premières et des taux de change.